提起领先EDA工具商,很多人印入脑海的是全球EDA三巨头而不会想到本土EDA工具商,其实,随着本土IC设计产业的飞速发展(据说今年要突破2000家IC设计公司!涌现出了海思、展讯这样的世界级IC设计企业),本土EDA工具厂商也在快速崛起,从昨天华大九天的发布新品来看,未来本土EDA企业在全球三分天下有其一并不是梦想。

“华大九天发布的全新物理设计时序优化与Silicon-aware Sign-off解决方案已经获得海思等了国内龙头IC设计企业的采用,打进这些企业我们不是靠民族牌而是真正的实力,我们的工具是在现场跟国外巨头PK后获得客户认可的。”华大九天副总经理吕霖表示,“现场PK结果是我们的工具可以大大帮助他们提升设计效率,这是因为我们用了不一样的思路。”

在发布现场,海思后端设计专家魏维、展讯后端设计总监陆炳华、中兴微电子后端设计专家陈友鹏等国内IC设计公司后端设计负责人到场祝贺华大九天新品发布,魏维、陆炳华、陈友鹏等在发言中特别感谢华大九天的分析工具帮助他们加速完成高性能CPU设计。

“我们很早就使用了九天的ICE后端时序分析工具,确实帮助我们在高级工艺处理器设计上节省了很多时间,一般后期做蒙特卡洛分析跑多个scnarica、上千个path几乎是人力难为了,感谢九天的新工具帮助我们大大提升了效率。”魏维在发言中指出,“我们希望华大九天未来继续推出更多工程用的好工具来!”

陆炳华、陈友鹏也表示利用华大九天的时序分析工具大大提升了设计效率。

那这款让本土IC设计师大赞的工具神奇在哪里?

STA分析的天生缺陷

我国著名国画家齐白石有句名言是:“学我者生,似我者死!”对于一个EDA工具商来说,如果只能单纯的模仿国际巨头的工具,则总是步其后尘难以突破,而且EDA领域专利壁垒森严,稍有不慎不是赔的倾家荡产就是锒铛入狱,要突破就要有新的思路和做法。

华大九天研发总监董森华昨天在发布会上全面详细地介绍了这款新工具----面向先进工艺SOC设计的全新时序优化解决方案ICExplorer-XTop 和SPICE级别快速准确Silicon-aware Timing Sign-off解决方案ICExplorer-XTime。---注意这里面的X不是发X音,而是发cross音,董森华解释说这是希望这款工具可以横跨很多应用。像X战警一样神奇。

董森华表示华大九天一直深耕时序收敛并引领了时序收敛技术,华大九天的ICExplorer系列产品(TimingExplorer 、ClockExplorer),是业界首款Physical-aware时序优化产品,为众多全球顶尖高端SOC芯片设计厂商采纳,已成功用于数十款16nm/10nm SoC芯片流片。

此次华大九天发布的下一代物理设计时序优化及签核解决方案,在上一代产品的基础上,进一步优化了软件架构和算法,不仅大幅提升性能,改进QoR,再次掀起“时序优化的革命”, 创造性地提出了Silicon-aware Sign-off 的解决方案。

“传统的时序分析都基于STA模型

STA --静态时序分析(Static Timing Analysis),简单定义如下:套用特定的时序模型(Timing Model),针对特定电路分析其是否违反设计者给定的时序限制(Timing Constraint)。),但是当半导体工艺进入FinFET时代,线宽发展到16nm以下以及更多采用低电压工艺时,这样的分析模型造成了良率下降提升了时间成本流片成本。”董森华指出,“现在基于STA的timing sign off的方法已经不适应现在设计需求,所以需要新的更好更快速更完美适应先进工艺适应IOT发展的新流程。”

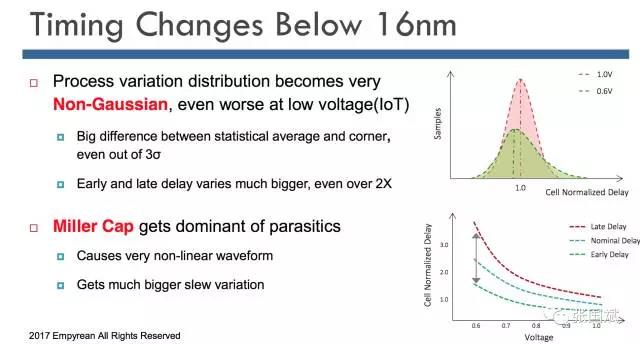

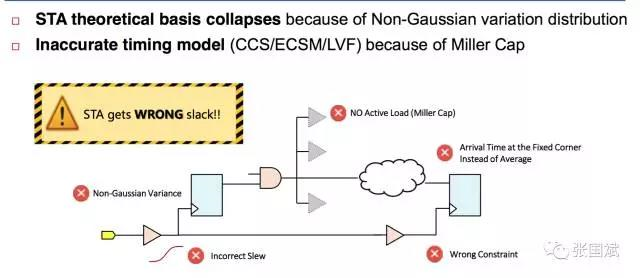

他指出在16nm工艺下,最重要的变化特性是器件的variation distribution呈现出非高斯特性,而STA的理论基础就是高斯分布,但实际上工艺参数已经不是高斯分布了,通常IC设计中的corner其实就是假设高斯分布的顶点正好落在统计分布的中心线上,通过对corner的分析来代表工艺统计的平均分析,不过在先级工艺下以及低电压下,高斯分布顶点和统计平均分布差异很大,所以基于STA 的功能sign off理论基础不复存在了!

另外,线宽变小以后米勒电容效应的危害变大了,在16nm工艺中,造成了更多的非线性变化,这造成了设计者无法准确评估时序特性,其结果是基于STA的时序分析方法不再准确,即便在先进设计中使用了各种OCV方法也改变不了精度,因为STA的基础是timing 库,但由于非高斯和米勒电容效应的影响,所以目前没有任何时序库可以代表实际效果,这样就造成了今天IC设计的困局。

这个影响到底有多大?据董森华估计STA和硅芯片精度误差是通常是3%,而到16nm工艺以后是5-6%,如果加上低电压的影响,则误差甚至可以超过10% ,这意味着要使用20%的margin 以及带来更多的人工成本、更多的面积来解决时序不精确问题

所以可以说STA设计造成了更多的浪费---大家要设计更多冗余来保证设计良率,所以设计师不断加Margin,这种滥用Margin导致冗余度多,另外在先进工艺下,时序变得很敏感,一点点的变化就引发了setup问题,为了解决这些问题,设计师只能花大量时间大量去迭代,这又错过了产品面市时间。

“我们今天要推的新品就是要打破STA的局限,打破现在的格局。跨越现在静态时序分析方法,提供更为准确的方式方式。”他强调。

新工具的核心是什么?

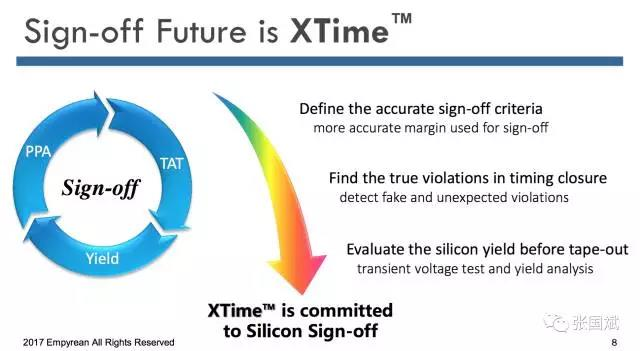

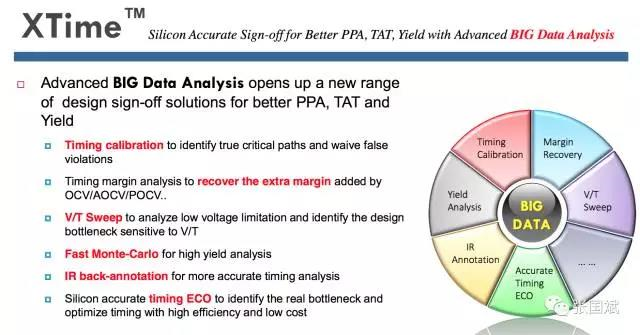

这个新品就是华大九天融合多年仿真技术积累以及结合大数据分析方法的ICExplorer-XTime,它在时序评估阶段可以准确评估时序,帮助设计师重新定义sign-off标准,并可以设置更合理的标准,帮助设计师在设计初期领先他人,还可以校准基于STA模型而造成的不准确时序。

此外,它还可以发现假的或者不期望的时序违规(timing violations),还可以在tape-out之前准确评估良率,发现设计良率是否符合三个西格玛还是五个西格玛要求,这太强大了!

为什么ICExplorer-XTime可以实现精准的时序收敛分析?

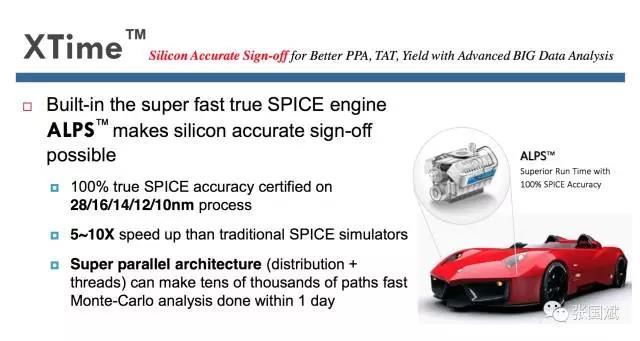

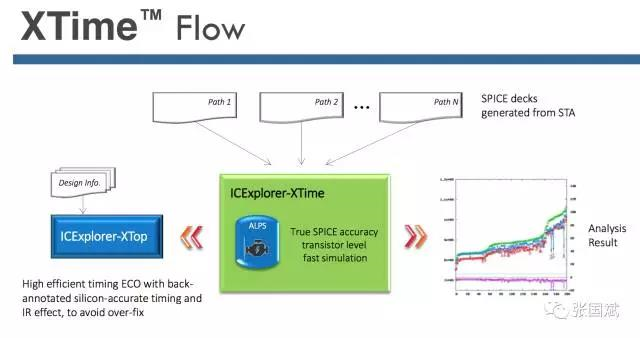

其理论基础就是采用了大家熟悉的SPICE仿真模型,这个模型目前仍被大量数字模拟设计采用,精度非常高,但是运行需要大量的时间计算资源。我记得毕业设计时做的是电视高频头的仿真优化,当时跑个结果需要几个小时时间,ICExplorer-XTime的SPICE级仿真为什么可以这么快?

这是因为它有个核心---SPICE级仿真引擎(ALPS™)!这是华大九天独立开发的引擎,是现场打败竞争对手的关键技术!按吕霖的说法这绝对是全球第一,中国独有!据传EDA巨头正全力研发类似引擎!

董森华解释说ICExplorer-XTime内嵌的SPICE级仿真引擎(ALPS™)拥有先进的智能矩阵求解技术,相比传统仿真器可提供5-10X的加速。全新的分布式并行化的体系架构,可以充分利用处理器硬件资源,快速完成仿真及结果大数据分析。“通过采用了超并行架构,通过分布式和多线程我们还可以对SPICE加速,例如做蒙特卡洛分析一万条path,用华大九天的工具一天可以完成,而采用其他工具,跑100条path都要半个月或者一个月时间!”董森华强调。

而基于仿真的大数据分析则可以把仿真结果更准确展示给客户,让客户知道时序的真实情况,由于大数据分析帮助客户打开了一系列时序sign-off手段,除了可以矫正精度,还可以通过XTime的V/T Sweep 知道SoC芯片在变电压情况下的工作情况,甚至可以去分析芯片单元在电压变化时的特性变化!还有超级电压下的工作极限寻找等。

可以帮助设计师更准确地评估硅级别的芯片状况。帮助设计师进一步提升设计的PPA性能、TAT周转时间以及良品率。

同时,ICExplorer-XTime提供了丰富的Silicon-aware Sign-off功能,例如关键路径的时序矫正、电路对电压及温度的敏感度分析,快速蒙特卡洛分析等,

而其工作流程是非常简单的,如下图所示

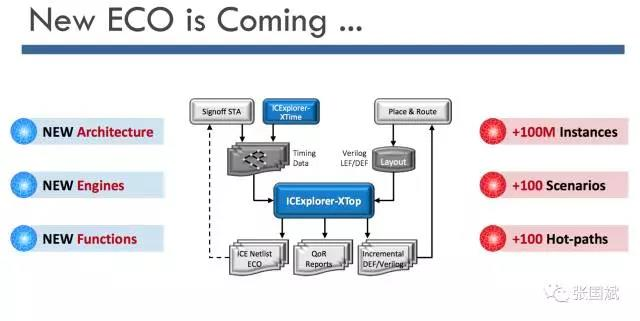

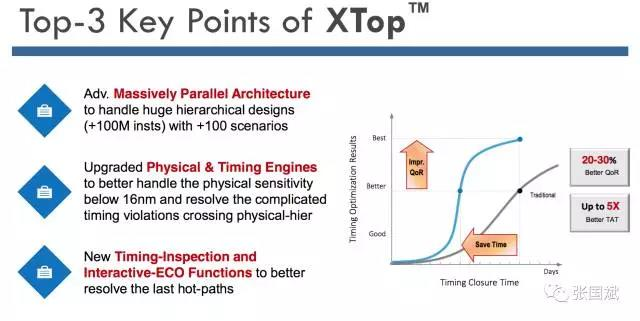

实际上,ICExplorer-XTime只是一个产品,昨天华大九天还发布了另一款新品ICExplorer-XTop--新一代的时序优化解决方案,它和ICExplorer-XTime一起使用,可以完美解决先进工艺下的时序收敛问题。“XTop从字面的意思就是超越自我永远领先,希望新的ECO方法给用户创造更大的价值。这个新的ECO产品采用了更新的架构。”董森华强调。“它致力解决的问题就是要解决超过一亿晶体管,100个scenarios的复杂设计难题--设计最后一公里的设计迭代问题。”

ICExplorer-XTop核心技术包括:

全新的分布式并行软件架构,更好的支持多角多模MCMM条件下各个工作场景,减少了大规模设计对内存的占用需求,进一步加快运算速度。设计优化前的准备过程支持增量化配置,时序优化的过程中可以随时保存或恢复会话场景,用户使用体验更加方便快捷。

在流程各个阶段通过并行加速设计,整个设计过程中不管芯片大小(不管1亿晶体管还是2亿晶体管),时序分析只跟导入的芯片中最大的block有关,对于超大规模设计的最大提升。而且可以在任何节点存储当时的状况,“此外,受益于并行架构,我们还可以提供增量式set up,其他方案每次优化都要把所有设计灌进去,而我们只需要把需要分析的blcok导入进去就可以获得完整的workspace进行后续的分析,可以极大提升数据准备的效率。”他特别指出。在流程各个阶段通过并行加速设计,整个设计过程中不管芯片大小(不管1亿晶体管还是2亿晶体管),时序分析只跟导入的芯片中最大的block有关,对于超大规模设计的最大提升。而且可以在任何节点存储当时的状况,“此外,受益于并行架构,我们还可以提供增量式set up,其他方案每次优化都要把所有设计灌进去,而我们只需要把需要分析的blcok导入进去就可以获得完整的workspace进行后续的分析,可以极大提升数据准备的效率。”他特别指出。

他也表示这次新工具把物理引擎都做了升级,Placement Engine 可以支持16nm、12nm、10nm、7nm设计,新的Routing Engine 可以更好的估计routing congestion 而Hierarchy Splicing Technology则解决了violations on crossing physical-hierarchy net。

而先进的物理分析引擎支持先进工艺下的物理约束、更好的处理布线拥挤问题,可以针对复杂层次化设计中逻辑管脚上的时序违反进行优化。

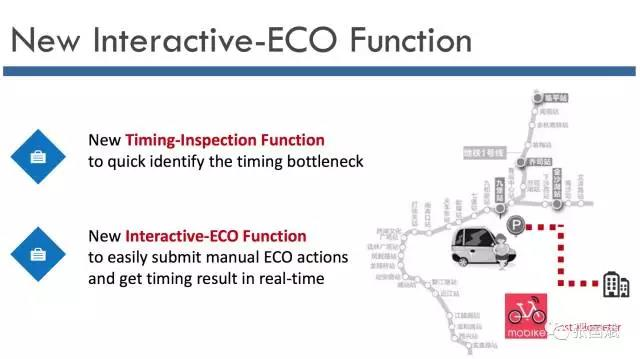

而强大的时序检查及交互式ECO功能,帮助用户快速修复最后阶段的hot-path。卓越的图形用户界面设计,强调用户体验,方便浏览版图和检查时序路径,完成交互式ECO的操作,并获得所见即所得的可视化结果报告。

这是结果对比,在提升效率方面非常显著!

中星微电子的陈友鹏在会后表示华大九天的工具对于大设计非常有帮助,Timing 收敛提升非常快,中兴微电子在16nm以后设计会考虑继续使用华大九天的工具。

吕霖表示其实严格说华大九天在88年就开始EDA工具开发了,已经有20多年的发展积累,见证了中国IC设计业的发展壮大,中国近2000家本土IC设计企业给华大九天带来了巨大的发展机遇,华大九天已经做好资本和技术准备,和客户一起开创EDA工具新未来!

中国蓬勃发展的集成电路应用市场给IP厂商、EDA工具厂商、IC设计公司、封测企业带来了发展大机遇,我们有理由随着“EDA神器”华大九天的ICExplorer-XTop与ICExplorer-XTime发布,华大九天将迎来更大的发展空间,祝愿本土IC设计产业茁壮成长!