(2015年11月20日,深圳)华大九天2015年技术研讨会在深圳软件大厦举行。大会由深圳市半导体行业协会承办,得到国家集成电路设计深圳产业化基地(深圳ICC)的悉心指导,并邀请到深圳市海思半导体、中兴微电子、晶门科技等公司的多位技术专家参与研讨。

在此次研讨会上,华大九天物理设计事业部总经理董森华正式发布了新一代10nm级高速并行仿真工具——ALPS,该方案已在晶门科技获得成功验证,大大提高仿真效率;并就数字SoC设计优化解决方案进行了全面探讨。

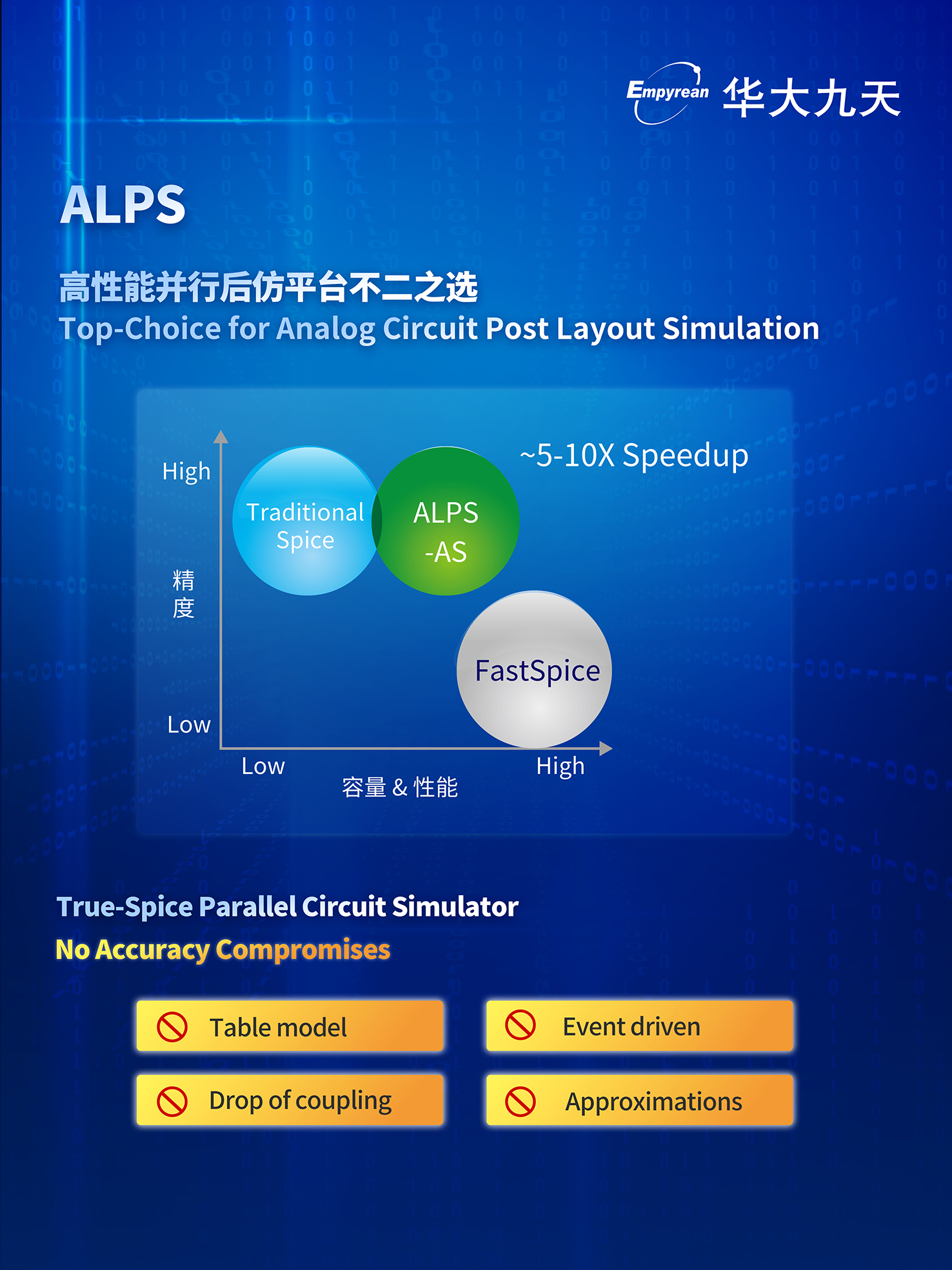

新一代全芯片高速仿真解决方案——ALPS

随着先进工艺节点的发展,IC设计变得越来越复杂,尤其是后仿电路的寄生器件规模越来越大。华大九天利用独有的新一代smart matrix solver,提供了高精度、高性能、高容量的并行spice仿真工具ALPS。 对于大规模的后仿设计,与目前市场的主流商用仿真工具相比,ALPS具有数倍到十数倍的加速效果,可大幅缩短IC产品开发周期。

高精度

ALPS不采用传统fast-spice技术,不使用任何模型简化技术,求解全电路方程,严格遵守Spice的收敛准则及步长控制方法,保证True-SPICE级别精度。

高性能

传统仿真工具在原有架构上添加了并行技术,而ALPS基于并行架构开发,更好的分配并行任务,适合大规模的并行计算。同时ALPS使用独有的smart matrix solver技术,根据矩阵特征自动选择最合适的矩阵求解器,极大地节省了矩阵求解时间,性能远超主流商用仿真工具。特别适合用于大规模模拟电路后仿真应用。

高容量

ALPS采用先进高效的内存管理方式,可应用于千万量级晶体管规模的top level True-SPICE级仿真。

此外,来自海思半导体资深工程师杨宇辉、中兴微电子著名后端专家李剑、资深工程师陈志荣及晶门科技晶片设计经理吕小康等技术专家还就华大九天海量版图高效处理平台Skipper、库单元及IP质量检查平台Qualib、时钟时序及功耗优化方案ICExplorer(包括ClockExplorer\TimingExplorer\PowerExplorer)进行案例分享。

今年,华大九天高速接口类及超低功耗IP已经在深圳ICC提供的IP平台上线,为深圳当地芯片设计企业提供更便利的本地化服务。

欲了解更多EDA解决方案及IP信息,请访问 http://www.empyrean.com.cn

[活动预告]在12月10日即将举办的中国集成电路设计业2015年会(ICCAD)上,华大九天将就以上EDA及IP解决方案进行展示,欢迎IC设计工程师保持关注,并诚邀赴会!